# Bigger, Faster, Better Resolution: Future TES Technology for SSRL Beamlines

IFDEPS April 1 2021

Galen O'Neil, galen.oneil@nist.gov

Donghui Lu

Jun-Sik Lee

**Dennis Nordlund**

Sang-Jun Lee

# SSRL 10-1 TES Upgrades

- **5.3x** effective area

- Funding from DOE Basic Energy Science

- Target install date ASAP 2021

- New TES Array + low temperature readout

- ~Better software integration, data plots available instantly

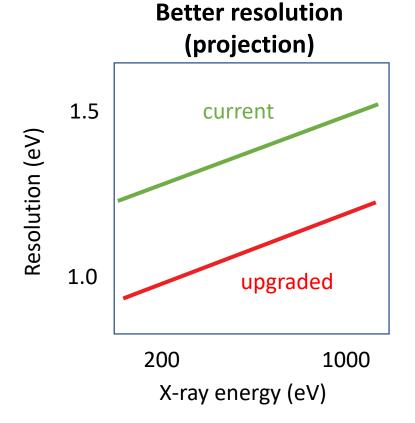

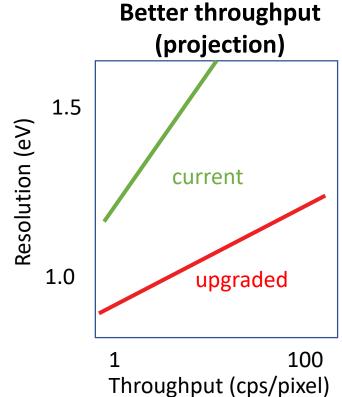

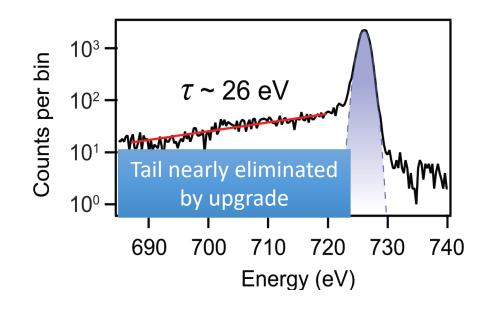

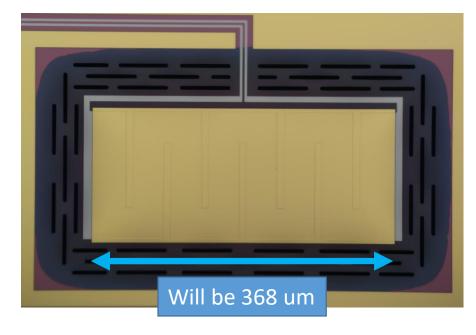

### SSRL 10-1 Pixels Compared

#### resolution

$$\Delta E \propto \sqrt{k_B T^2 C}$$

### Current

Tc ~110mK Mo/Cu Bilayer Bi plating

- Weber, 2020, Superconductor Science and Technology

- Morgan, 2017 Applied Physics Letters

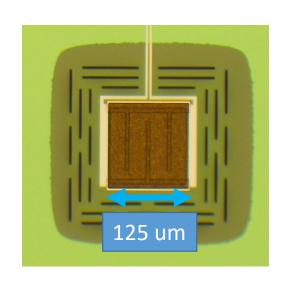

Tc ~75 mK Mo/Au Bilayer

#### Au has:

- More area for same heat capacity

- More x-ray stopping power

- More consistent fab

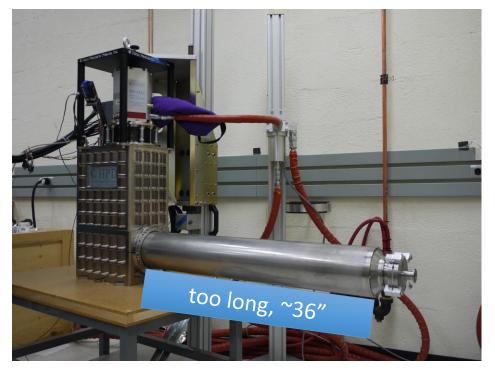

### SSRL 13-3 Upgrades

- Would like to follow 10-1, dependent on DOE funding

- Cryogenic improvement: Increase hold time (8->20+ hours)

13-3 now

change to match 10-1

10-1

UIUC Abbamonte, APS Rodolakis, McCheseny

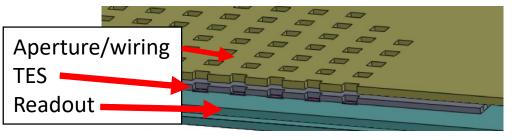

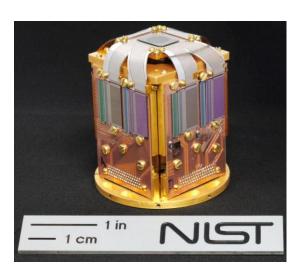

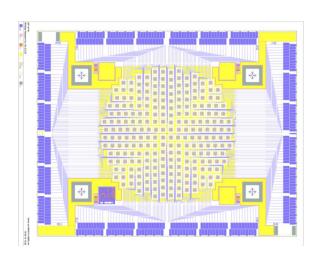

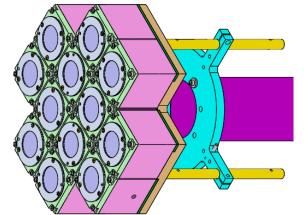

## To 10k pixels for LCLS2 and beyond

soon

### integral readout with alternate ucal tech

Space per wirebond  $\approx 1/\sqrt{N}$

Tiled arrays

and/or

### integrated 3d fabrication