### AZImuthal INTegration for fast X-ray area detectors on FPGAs

Carl and Brian – both NBI, Carl is a phd student in X-ray imaging applications for food industry project and Brian is an e-Science professor at NBI

Artur – physics, CERN, MAX IV network and infrastructure team

Kenneth – expert in FPGA languages, 'inventor' of SME<sup>\*</sup>, assistant prof. at NBI former eSSENCE postdoc at MAX IV

Zdenek – MAX IV scientific sw, x-ray scattering data processing

\*SME: Synchronous Message Excange: https://sme-hdl.org

### **Azimuthal integration**

#### why on FPGA ?

# <sup>2nd</sup> Scientific part can be separeted

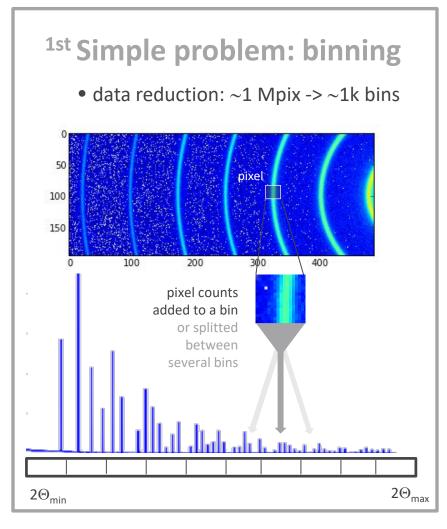

- easy for "static" detectors

- non-integer arithmetic needed for scientific accuracy

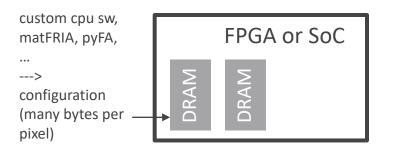

- pixel-bin "routing/mapping" as well as real value weights and pixel corrections can be calculated in advance and stored in device memory (high throughput -> requirements on dev-mem)

## **Azimuthal integration**

#### on FPGA ?!

### <sup>4th</sup> binning/histograming/AZINT – important algorithms

- crystallography:

- background estimation

- ice-ring removal

#### <sup>n-th</sup> non-synchrotron

- portable instruments

- space applications:

- limitted bandwidth for data transfer

- energy efficiency

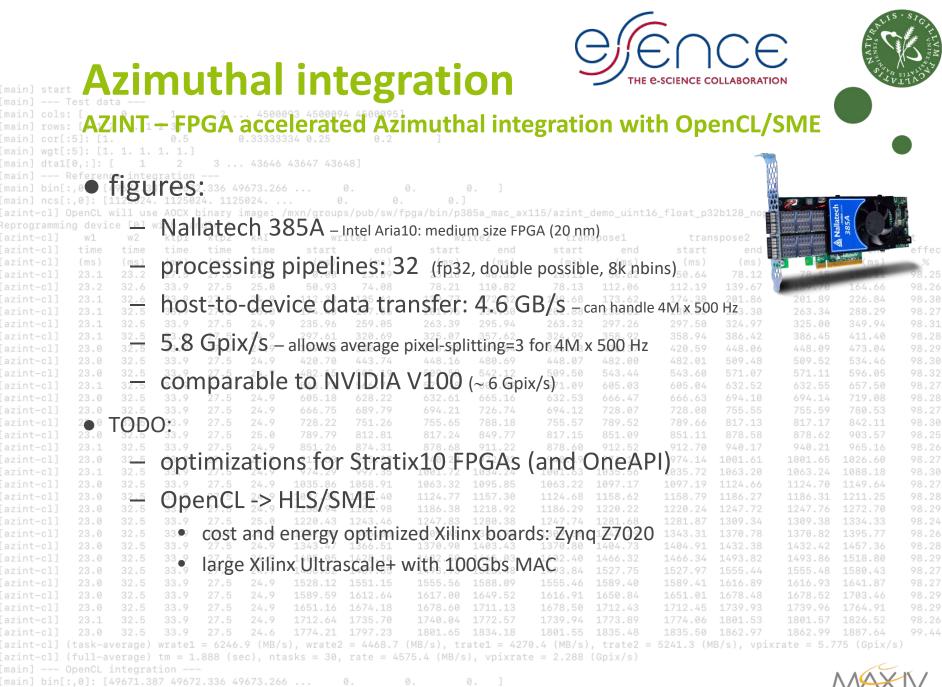

### **Azimuthal integration**

#### **FPGA implementation**

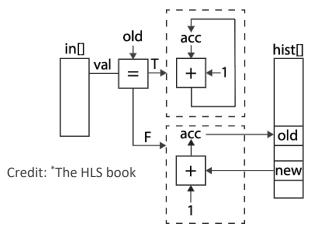

- a simple 3 stage pipeline at FPGA

- ref: PREFIX SUM AND HISTOGRAM in Kastner, Matai, Neuendorffer: *Parallel* \**Programming for FPGAs - the HLS book*, <u>http://kastner.ucsd.edu/hlsbook/</u>

- in HLS can be fully pipelined

- initial implementation in SME: <u>github.com/bh107/SME-Binning</u>

- Xilinx Zynq Z7020 at 100 MHz: 1 Gpix/s (10% util. per processing unit)

- Xilinx Kintex Ultrascale+ xcku5p at 590 MHz: 20 Gpix/s (3% util. per unit)

- floating point:

- single loop with HLS + bitonic-merge

- with OpenCL: <u>gitlab.maxiv.lu.se/compute-fpgas</u>

- note: result stored in BRAM, often high *nbins* (~10k) required which can be also limiting factor

[main] ncs[:,0]: [1125024. 1125024. 1125024. ...

[main] Test passed: True