### **IWORID** July 5<sup>th</sup> 2005, ESRF, GRENOBLE

# FLIP CHIP INTEGRATION: STATUS AND FUTUR TRENDS

www-leti.cea.fr

## OUTLINE

- INTRODUCTION

- What is packaging, the different levels

- Evolution of packaging

- The Flip chip technology

- DIFFERENT FLIP CHIP METHODS

- Associated technologies

- Advantages and Limitations

- INNOVATIVE TECHNOLOGIES

## OUTLINE

- INTRODUCTION

- What is packaging, the different levels

- Evolution of packaging

- The Flip chip technology

- DIFFERENT FLIP CHIP METHODS

- Associated technologies

- Advantages and Limitations

- INNOVATIVE TECHNOLOGIES

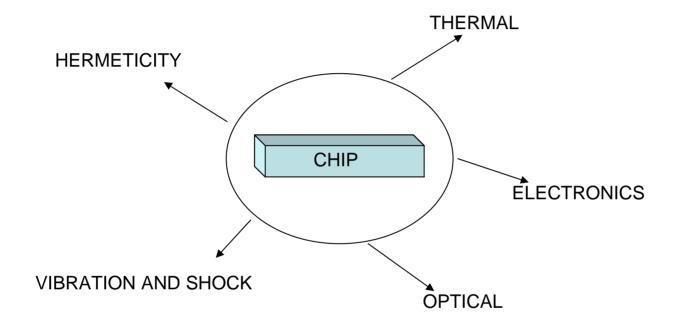

# What is Packaging

æ

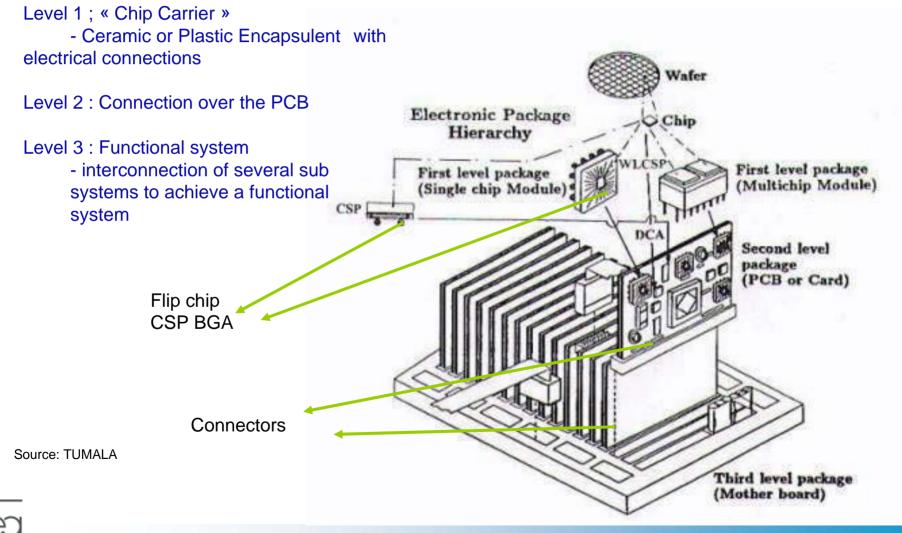

# Different packaging levels

Level 0 : Silicon Chip - Integrated Circuit etched on a Silicon Wafer

## OUTLINE

- INTRODUCTION

- What is packaging, the different levels

- Evolution of packaging

- The Flip chip technology

- DIFFERENT FLIP CHIP METHODS

- Associated technologies

- Advantages and Limitations

- INNOVATIVE TECHNOLOGIES

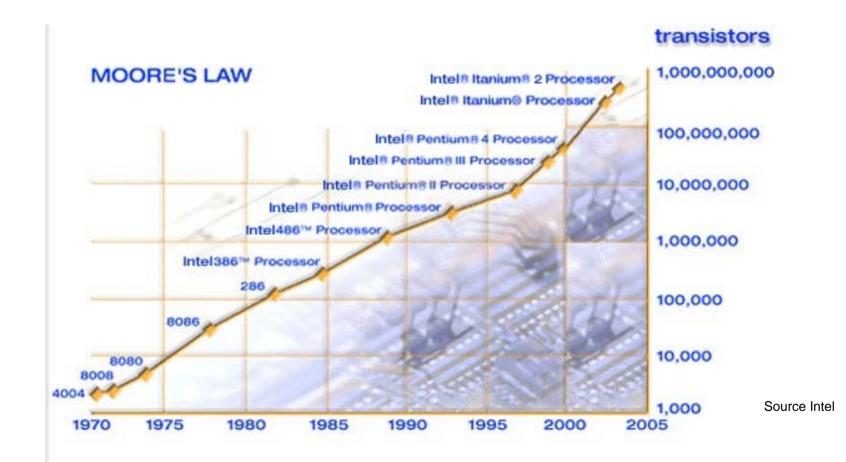

### Increased Chip Density

œ

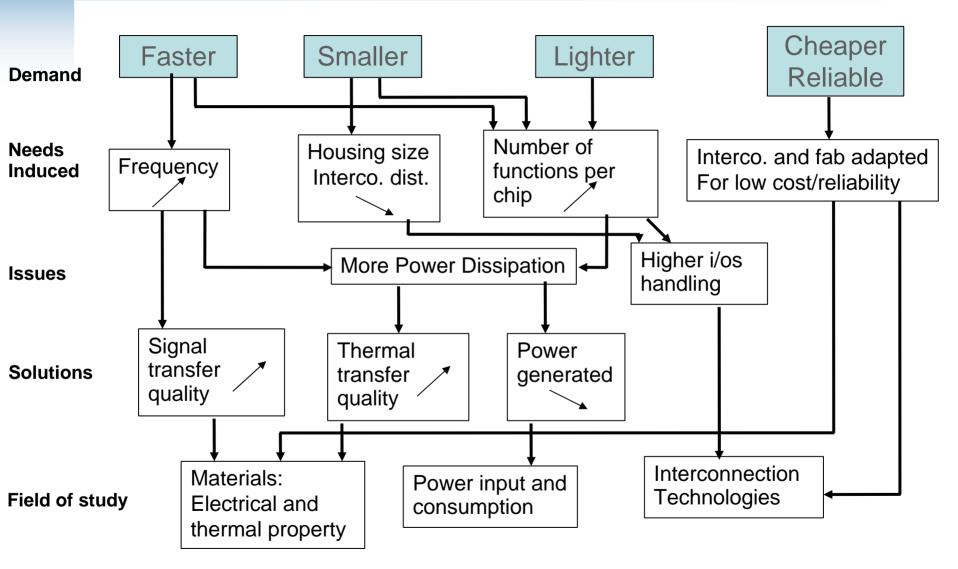

### Packaging: New Requirements

Source: M. Massena

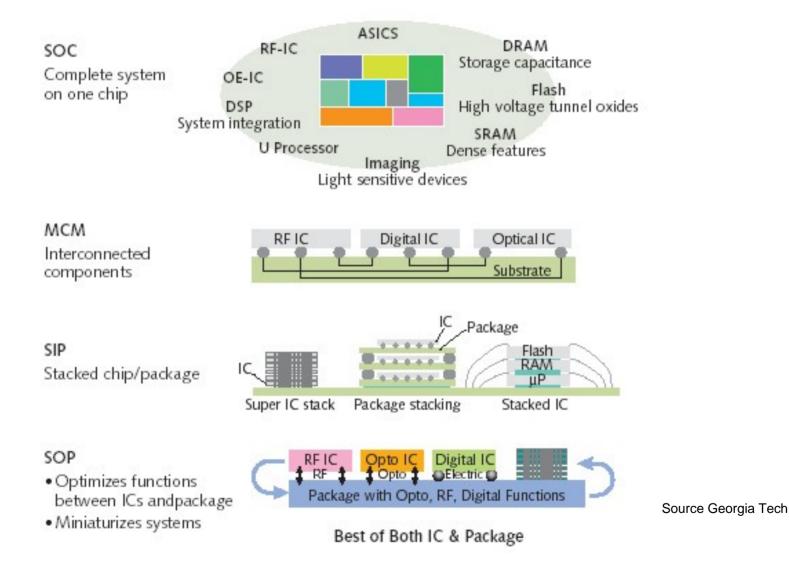

### SOP, SiP, MCM, SOC : lots of solutions

## OUTLINE

- INTRODUCTION

- What is packaging, the different levels

- Evolution of packaging

- The Flip chip technology

- DIFFERENT FLIP CHIP METHODS

- Associated technologies

- Advantages and Limitations

- INNOVATIVE TECHNOLOGIES

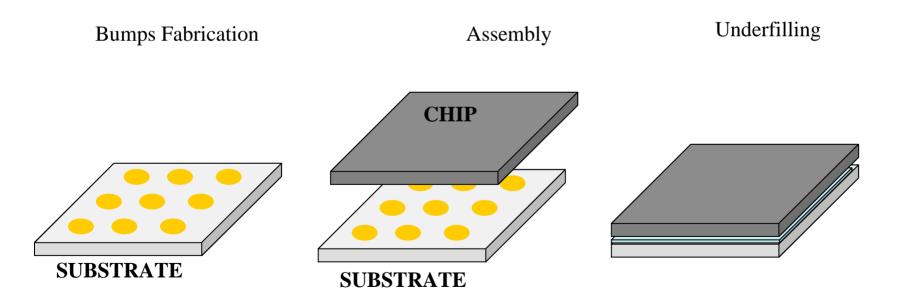

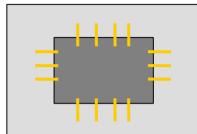

## What is Flip Chip

- Face down Electrical connection

- Chip over a substrate

- Array type connection (Not peripheral) using bumps

- Usually with an **underfill** (Reliability)

## A little bit of History

• Flip chip: invented by IBM in early 60's Controlled Collapse Chip Connection (C4- 1964)

3% wafers produced worldwide used for flip chip

Underfill introduced

10% wafers produced expected to be used for flip chip

### Flip Chip vs Wire Bonding

#### NUMBER OF I/O's

#### Smaller pitch

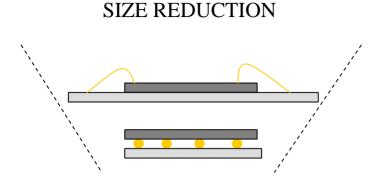

### • Flip Chip

- Size reduced

- Higher integration

- Shorter connection length

- Smaller pitch

- Self alignment

- collective process

- Efficient heat dissipation

### Wire Bonding

- Industrially proven

- Moderate cost

- Reliability

- Compatibility (housings, connectors)

- Standard metallurgy (no post process)

## OUTLINE

- INTRODUCTION

- What is packaging, the different levels

- Evolution of packaging

- The Flip chip technology

- DIFFERENT FLIP CHIP METHODS

- Associated technologies

- Advantages and Limitations

- INNOVATIVE TECHNOLOGIES

### Flip Chip : The different techniques

- Solder bump Flip Chip

- Stud bump Flip Chip

- Polymer bump Flip Chip

- Anisotropic Conductive film Flip Chip

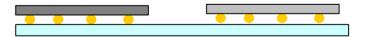

Chip over circuit

Chip and circuit over a substrate

# Solder Bump Flip Chip: The different steps

- ASIC and chip Post Process

- Solder bump deposition

- Solder Reflow

- Flip Chip assembly

- Underfilling

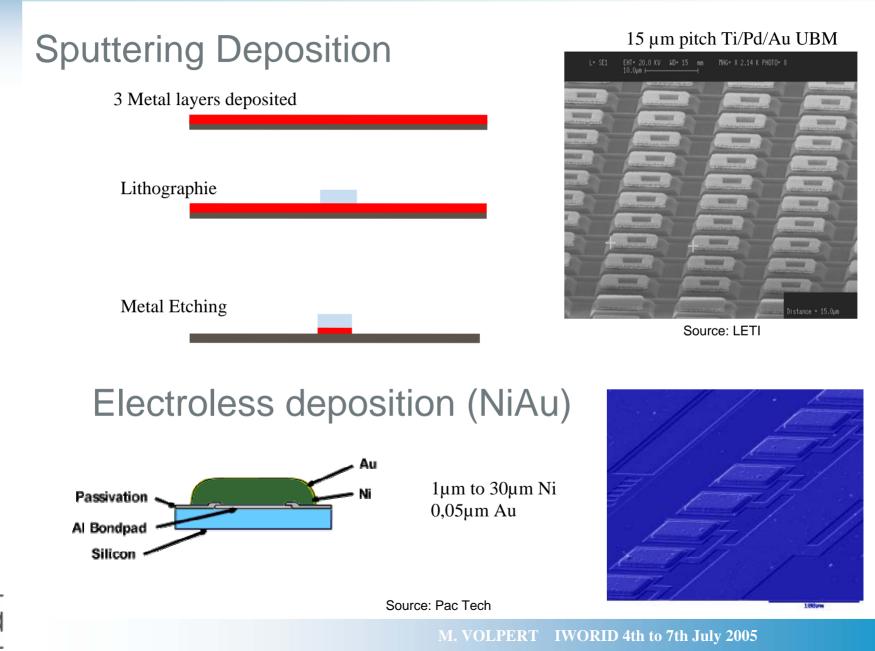

## Solder Bump Flip Chip: The Post Process

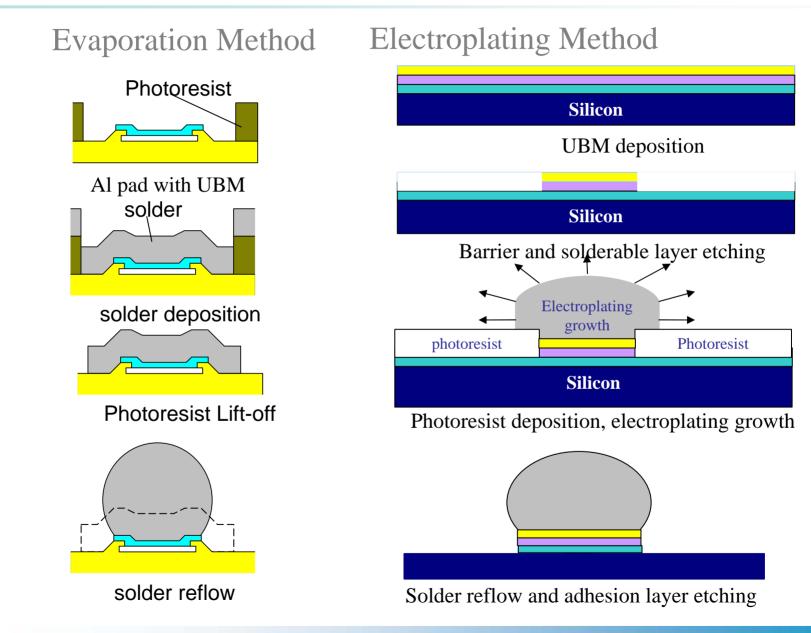

### Solder deposition and Solder Reflow

### Solder deposition and Solder Reflow

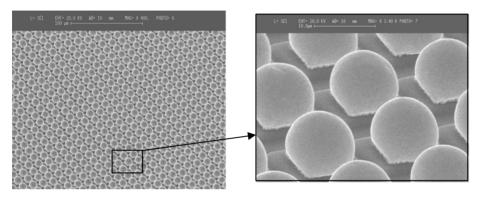

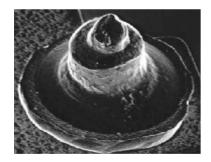

### Example of indium vapor deposition at leti

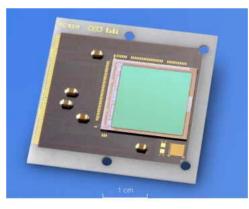

#### Méga Pixel IRFPA 1024 x 1024 : pitch =15 µm

Indium Micro-bumps (SEM Photography)

Spectral band: 3 - 5  $\mu m$  - Cutoff frequency: 5.5  $\mu m$

Night view Operability 99.8% NETD 20mK

# Solder deposition method comparison

|   |                 | Advantages              | Disadvantages      | Size       |

|---|-----------------|-------------------------|--------------------|------------|

| • | Evaporation     | - thin film process     | - cost, time       | 10 µ-100 µ |

|   |                 | uniformity, flexibility |                    |            |

| • | Electroplating  | - low cost,fine pitch   | - flexibility      | 10-200 µ   |

|   |                 |                         |                    |            |

| • | Screen Printing | - cost, simplicity      | - pitch limitation | 150-1000 µ |

|   |                 | production              |                    |            |

| • | Jet printing    | - limited number of     | - pitch limitation | > 150 µ    |

|   |                 | Bumps, no mask          |                    |            |

|   |                 |                         |                    |            |

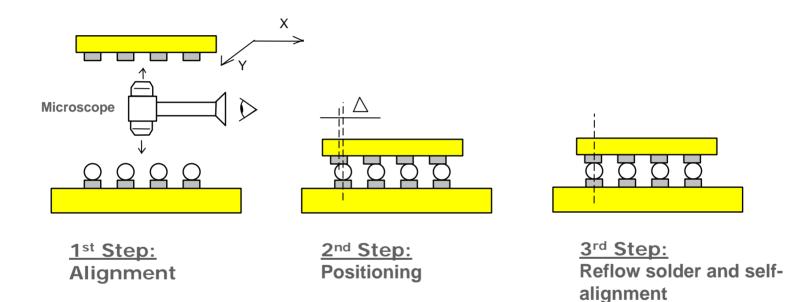

## **Solder Flip Chip Assembly**

### A three step process

### Solder Flip Chip: Associated Issues

- Temperature process: CTE mismatch

- Flux activated process: cleaning issues

- Large chip size: constraint, shear stress, reliability issues

- Yield: underfilling step necessary

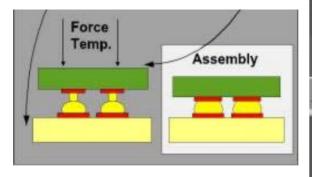

## Flip Chip using Stud Bump

- Conductive gold bumps on the die

- Directly on the Al pad

- Thermomechanical or Adhesive attachment

### Gold Stud Bump

Source: www.flipchips.com

Thermocompress ion assembly

Source: IZM

# Stud Bump Flip Chip:

### **Advantages**

- No wafer post process

- Bumping equipment widely available

- No fluxing

### Limitations

- Serial process (low to medium volume production, 24 bumps/sec.)

- No self-alignement

- Minimum Pitch 50-60 µm

- High Temperature & Force applied

# Polymer Flip Chip

### Principle

- Conductive particles filled adhesive

- Particles: Typically Silver

### Dispense

- Dispensing

- Screen Printing

- Assembly

- Curing

### Advantages

- Low temperature process

- Low cost

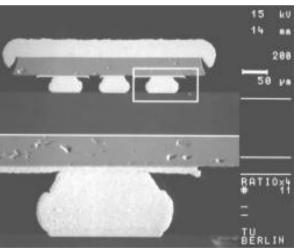

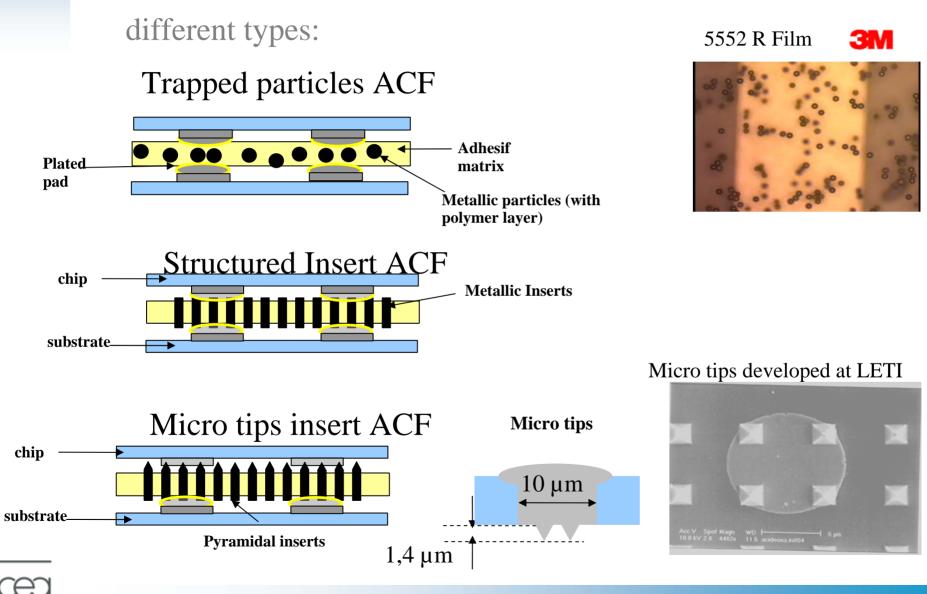

## Flip Chip with Anisotropic Conductive Film

# ACF Flip Chip

### **Advantages**

- No underfilling step

- Low temperature process (100°C)

- No post process with micro tips inserts

### Limitations

- Fine pitch

- Post process

- No self alignment

- Pressure applied

- Electrical contact

## OUTLINE

- INTRODUCTION

- What is packaging, the different levels

- Evolution of packaging

- The Flip chip technology

- DIFFERENT FLIP CHIP METHODS

- Associated technologies

- Advantages and Limitations

- INNOVATIVE TECHNOLOGIES

#### Leti Issues and Limitations

- CTE Mismatch

- Size limitation

- Reliability issues

- Small Pitch

- Alignment

- Cleaning

- Yield

- No inspection possible

- Circuit tiling

- Need solution for 3D Interconnection

- Cost

# Comparison of the Different Methods

|                        | DISPENSE<br>AND                                                                                           | PITCH                         | CONTACT<br>RESISTANCE                 | ASSEMBLY AND<br>TEMPERATURE                                                                                         | RELIABILITY                                                         | COST                                                                        |

|------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------|

| SOLDER<br>FLIP CHIP    | PROCESS<br>Screen printing,<br>Electroplating,<br>vapor<br>deposition, jet<br>dispensing.<br>Post process | 150μm<br>15 μm<br>and<br>over | 1.2 mΩ                                | Depends on solder<br>Reliable low<br>temperature solder: In<br>180°C process<br>Self alignment<br>Cleaning required | Reliable with<br>underfilling<br>Repairable                         | Depends<br>on solder<br>Expensive<br>with In                                |

| STUD BUMP<br>FLIP CHIP | required<br>Standard wire<br>bonding<br>equipment<br>No post process                                      | 60 µm                         |                                       | Over 200°C<br>Pressure applied<br>(75to100g/bumps)<br>No self alignment<br>No cleaning                              | Reliable<br>Not repairable                                          | 40\$/wafer<br>with<br>250000<br>bumps/wa<br>fer<br>source:<br>flipchips.com |

| POLYMER<br>FLIP CHIP   | Screen printing,<br>dispensing<br>Post process<br>required                                                | 125<br>μm                     | 5-10 mΩ                               | <100°C<br>No self alignment<br>No cleaning                                                                          | Limited<br>reliability for<br>dense<br>connection<br>Not repairable | Low cost                                                                    |

| ACF                    | Commercially<br>available films<br>Post process<br>required                                               | 50µm                          | 50 mΩ<br>( with 10<br>particles/pads) | 100°C<br>Pressure applied (15-<br>30 kg/cm <sup>2</sup> )<br>No self alignment<br>No cleaning required              | Limited<br>reliability for<br>dense<br>connection<br>Not repairable | Low cost                                                                    |

## OUTLINE

- INTRODUCTION

- What is packaging, the different levels

- Evolution of packaging

- The Flip chip technology

- DIFFERENT FLIP CHIP METHODS

- Associated technologies

- Advantages and Limitations

- INNOVATIVE TECHNOLOGIES

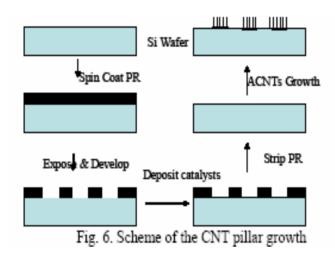

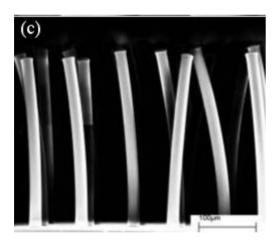

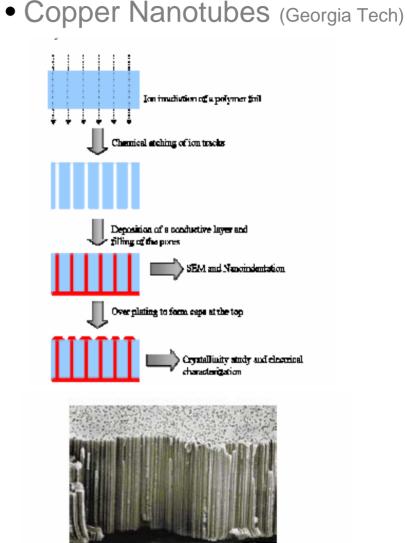

# New Flip Chip approach: Nano-connections

Carbon Nanotubes (Georgia Tech)

Figure 2: SEM image of side view of the etched polymeric membrane

# New Flip Chip approach: Nano-connections

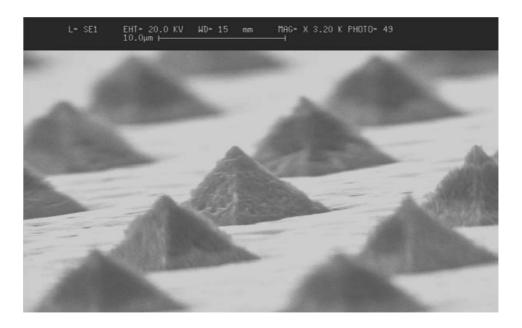

### • Solder Micro Tips (LETI)

- Fabrication demonstrated

- Assembly tested

- Fluxless assembly

- No underfill

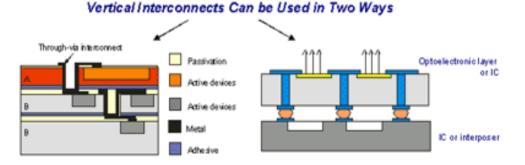

### 3D-Interconnections

- Based on through vias filled with metal (Cu)

- Strong technical challenges (vias, vertical wall metalization and passivation)

- Cell phone application (Japan)

- Exemple: MCNC Research Center:

#### Stacking of Device Layers

Typically:

- via diameter 5-10 μm

- Via pitch 25-50 µm

- Device layer thickness 20-50 μm

#### Via Aspect Ratio 5-10

#### Backside contacts w/flip chip

Typically:

- via diameter 50-100 μm (bond pad)

- Via pitch dependent on application

- Wafer thickness 300-500 µm

### Conclusion: Future Integration Trends

- Total Integration with SOC

- Very complexe

- Mix backend and frontend technologies

- Development of Wafer Level Packaging and SIP

- More and more heterogeanous functions on the same substrate (MEMES, MOEMS, IC's)

- Denser packaging: 3D connections

- New connection technique for Flip Chip assembly

### Thanks for your attention

# **QUESTIONS** ?

www-leti.cea.fr